Voltar aos Projetos Realizados

Voltar aos Projetos Realizados

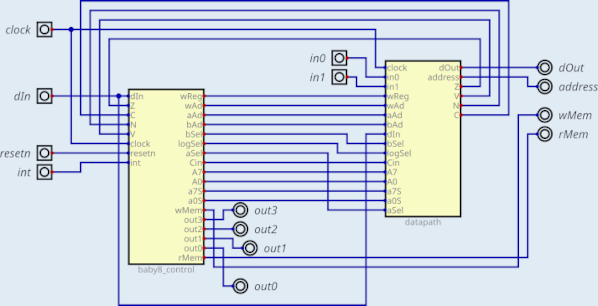

Processador Baby8

- Ano: 2024

- Titulo Original: Design and Evaluation of Open Source Soft-Core Processors

- Revista: Electronics - Basel

- Editora: MDPI

- Autores: Mario Gazziro, Jecel Mattos de Assumpção Jr, Oswaldo Hideo Ando Jr, Marco Roberto Cavallari, João Paulo Carmo

- Anexos:

RESUMO: A vantagem dos FPGAs reside na capacidade de implementar uma solução totalmente em hardware para interface com vários dispositivos de entrada/saída (E/S). Cada bloco pode trabalhar em paralelo com todos os outros, simplificando a satisfação das restrições de tempo. No entanto, esta utilização de hardware consome recursos FPGA que de outra forma poderiam ser alocados para o projeto primário. Uma alternativa envolve o emprego de um pequeno processador "soft-core" que implementa E/S em software. Com o objetivo de projetar e avaliar um novo e minúsculo processador soft-core otimizado para recursos FPGA em E/S, um novo processador chamado Baby8 foi desenvolvido. É um processador soft-core CISC de 8 bits otimizado para uso reduzido de recursos da FPGA, incluindo tamanho de programa para aplicativos de 8 bits. O número de instruções não é grande, mas qualquer instrução pode acessar locais de memória arbitrários. O desempenho e recursos de utilização do processador recém-projetado são avaliados e comparados com uma variedade de outros processadores soft-core. Os resultados demonstram seu desempenho competitivo, alcançando uma média frequência máxima de clock de aproximadamente 57 MHz e consumo de energia de cerca de 2mW. Além disso, conservou quase metade dos recursos dos FPGAs em utilizados na implementação.

ABSTRACT: The advantage of FPGAs lies in the ability to implement a fully hardware solution for interfacing with various input/output (I/O) devices. Each block can work in parallel with all the others, simplifying the satisfaction of timing constraints. However, this hardware utilization consumes FPGA resources that could otherwise be allocated to the primary project. An alternative involves employing a small "soft-core" processor implementing I/O in software. With the goal to design and evaluate a new tiny soft-core processor optimized for FPGA resources in I/O , a novel processor named Baby8 is developed. It is an 8-bit CISC soft-core processor optimized for reduced FPGA resources including program size for 8-bit applications. The number of instructions is not large but any instruction can access arbitrary memory locations. The performance and resource utilization of the newly designed processor are evaluated and compared with a variety of other soft-core processors. The results demonstrate its competitive performance, achieving an average maximum clock frequency of approximately 57 MHz and a power consumption of around 2mW. Furthermore, it conserves nearly half of the FPGA resources in implementation.